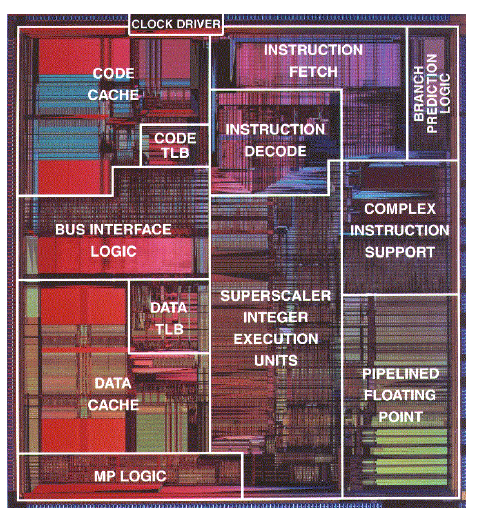

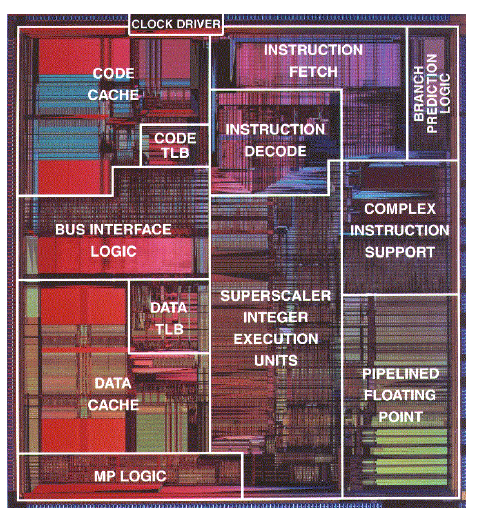

I. Increasing Complexity in Multi-Voltage Designs

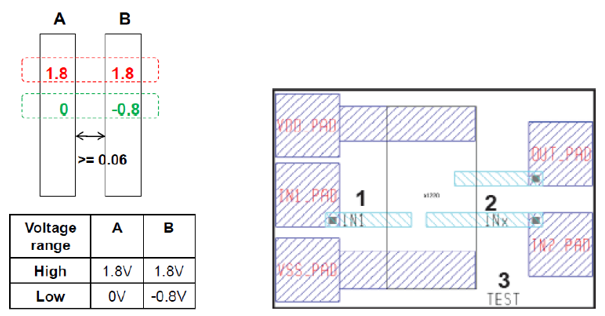

Modern dies contain multiple voltage domains. Voltage differences (ΔV)

between regions introduce spacing challenges and dielectric stress concerns.

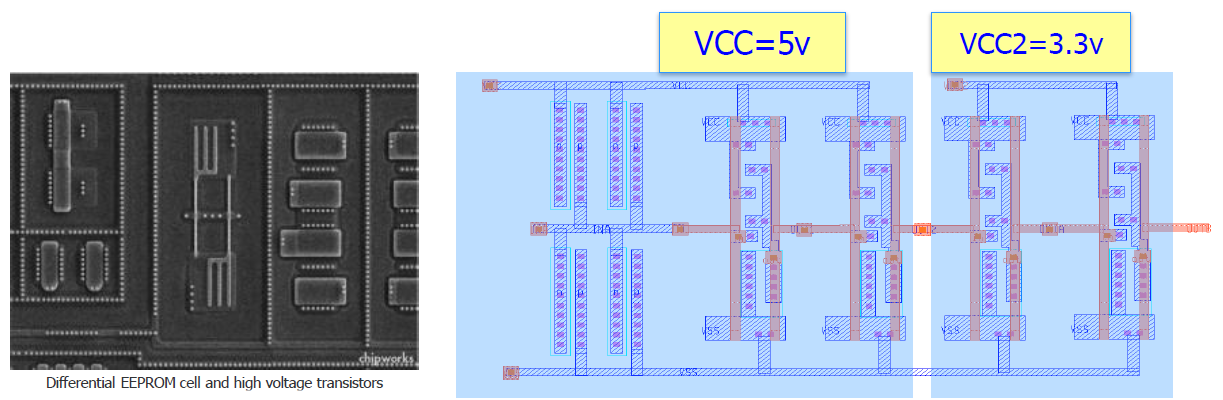

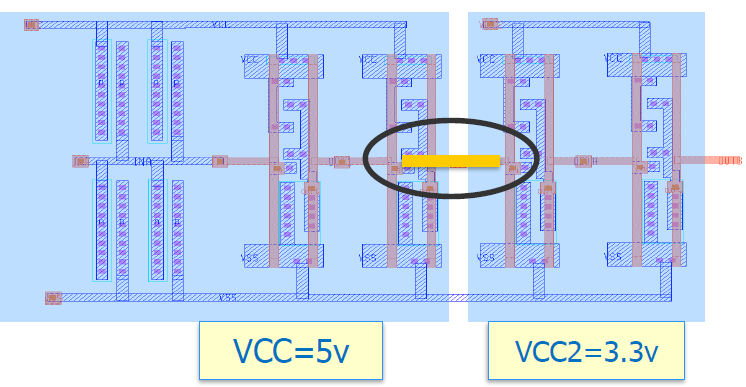

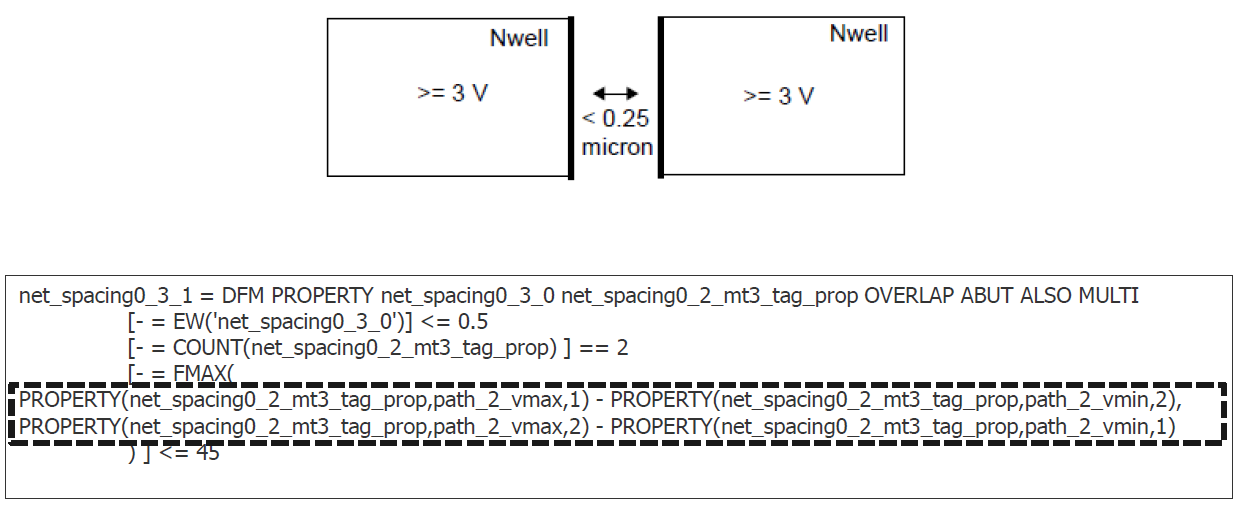

II. Voltage-Aware Spacing Requirements

Spacing rules must vary depending on voltage combinations:

5V ↔ 5V

3.3V ↔ 3.3V

3.3V ↔ 5V

Greater ΔV requires larger spacing to prevent breakdown.

III. Limitations of Marker Layer Methodology

Traditional approaches relied on marker layers to isolate voltage regions.

However, advanced nodes introduce:

• More voltage domains

• Cross-domain routing

• Increased rule complexity

• Human-error risk

IV. Text-Based Voltage Annotation

Voltage annotations enable deterministic checking by assigning

voltage properties directly to nets.

Advantages:

• Reduced dependency on CAD marker layers

• Improved reliability

• Better automation

V. Deterministic Voltage-Aware DRC Flow

Voltage propagation and spacing verification are integrated

into connectivity-aware checking.

Voltage-aware DRC provides deterministic, scalable, and

reliability-driven spacing verification for multi-domain designs.

As nodes scale and power domains multiply, voltage-based rule

evaluation becomes mandatory for robust sign-off.